单片集成电路(IC)是指所有功能都在单个硅芯片(也称为芯片)上实现的电路。使用极紫外(EUV)光刻工艺的芯片最大实际尺寸约为25mmx25mm=625mm2。虽然可以制造更大的芯片,但其产量开始迅速下降。因此,当今数十亿晶体管器件的一种解决方案是将设计分解成多个较小的芯粒,安装在硅中间膜上,以单个封装形式呈现。在这种情况下,较小的芯粒被称为 chiplet 或 tiles,而最终器件则被称为小芯片组。

采用基于小芯片的方法具有多种优势,包括提高产量、降低芯片成本,以及在最佳工艺技术上实现不同功能的能力。此外,由于设计人员可以针对不同的应用选择合适的小芯片,因此灵活性和定制选项也得到了提高。这种方法提高了可扩展性,因为更多的小芯片可以满足更高的工作负载需求,并通过在不同产品中以不同组合重复使用现有小芯片来缩短上市时间。

像英特尔等几家公司多年来一直在使用基于小芯片的技术,但这些公司通常对整个设计流程拥有完全控制权。多芯片系统开发人员的梦想是能够从多个供应商处获取硬小芯片 IP,就像当今的 SoC 设计人员使用第三方供应商的软 IP 功能一样。

人们普遍认为小芯片将为未来的设计提供动力,但我们所说的 "未来 "指的是什么呢? 就在一年前,业内人士还预测未来五到六年才会广泛采用。然而,最近有几家公司推出了芯片组产品,表明采用芯片组技术的时间可能比预期的要早。

未来的许多小芯片在尺寸和复杂性上都将超过今天的IC(ASIC、ASSP 和 SoC)。此外,当今大多数IC都采用了某种形式的片上网络(NoC),它可被视为跨越整个集成电路的互连 IP。这些基于 NoC 的芯片如何相互通信?

D2D互联方案

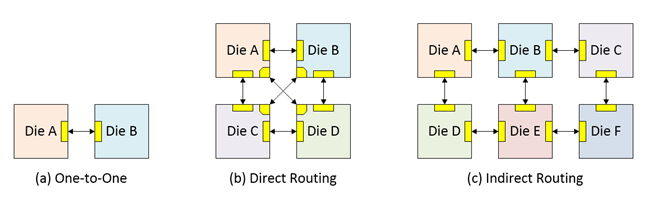

可以识别各种小芯片到小芯片的互连场景。这种互连通常称为Die-to-Die (D2D),以避免与印刷电路板 (PCB) 级别的芯片到芯片 (C2C) 互连混淆。首先,考虑一些非相干 D2D 互连的可能性(图 1)。

图 1以下是三个非相干互连示例。来源:Arteris

如图 1a 所示,最简单的方案只涉及两个直接 D2D 连接的芯片。一个更复杂的例子涉及更多的芯片(图 1b),仍然是直接 D2D 连接和启动时的静态映射模式配置。在涉及芯片跳转的间接 D2D 路由情况下(图 1c),有两种可能性:在启动时进行静态映射模式配置或在运行时进行动态映射模式配置。

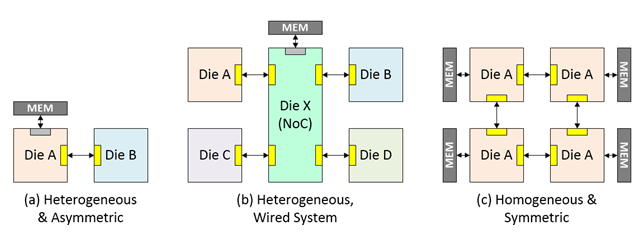

接下来,考虑一些相干 D2D 互连的例子(图 2)。在这种情况下,除了处理器和加速器缓存等任何片上存储器外,我们还展示了 DDR 等外部存储器 (MEM) 的可能部署情况,这些存储器由较大的灰色矩形表示。这些存储器是多芯片系统封装的外部存储器,需要片上存储器控制器 IP,如较小的灰色矩形所示。

图 2 上图显示了三个相干互联示例。资料来源:Arteris

相干互连的最简单形式是异构和非对称,如图 2a 所示。在这种情况下,有一个明确的主机芯片与外部存储器相连。在另一端,我们看到的是同构对称架构(图 2c)。在这种情况下,每个芯片都能与自己的内存和其他芯片的内存对话。显然,这很快就会变得复杂。此外,设计人员还需要格外注意与 D2D 通信相关的瓶颈和延迟问题。

我特别感兴趣的是,当我参加在比利时鲁汶举行的全球首个以汽车为中心的 Chiplet 活动时,有人谈论拥有一个特殊的 NoC Chiplet,为所有其他 Chiplet 提供对共享内存的访问同时也充当一种仲裁者(图2b)。这个想法是让这个小芯片(图中显示为 Die X)充当集线器。其他小芯片正在竞争对中央共享内存的访问,因此有必要调节缓存一致性。这种情况允许设计人员将智能构建到集线器中。

更深入的 D2D 互连研究

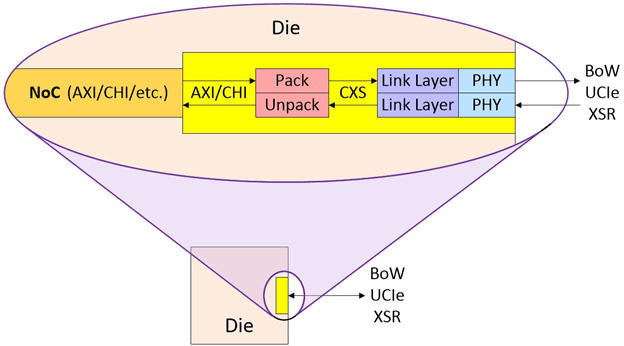

让我们更深入地了解一下 D2D 互连(图 3)。我们将从小芯片本身使用的 NoC 开始。设计人员可以使用各种 NoC 技术。例如,Arm 的高级微控制器总线架构 (Advanced Microcontroller Bus Architecture, AMBA) 采用了非相干高级可扩展接口 (Advanced eXtensible Interface, AXI) 协议和相干集线器接口 (Coherent Hub Interface, CHI) 协议。

图 3 凸显 NoC 的D2D互连示例(左)。资料来源:Arteris

假设设计人员使用 AXI 或 CHI 等 NoC 协议,或者可以生成和接收 AXI 或 CHI 流量的 NoC IP,则任何出站流量都必须打包为某种流接口格式(如 CXS)。然后,打包的数据被传递到链路层控制器和相关的 PHY。

物理层将使用 Bunch of Wires (BoW)、Universal Chiplet Interconnect Express (UCIe) 或 Synopsys eXtra Short Reach (XSR) 等技术来实现。同样,入站流量将通过关联的 PHY 和链路层并解包到 AXI 或 CHI。

早期,多种选择

值得注意的是,我们仍处于这项技术的早期阶段,人们仍在摸索各种方法,让每件事和每个人都能共同发挥作用。例如,由于小芯片可能采用来自不同第三方供应商的 IP 块,而且每个 IP 块可能采用自己的数据宽度、时钟频率和互连协议,因此 NoC 可能需要适应业界已定义和采用的多种标准协议,如 OCP、APB、AHB、AXI、CHI、STBus 和 DTL。

为了解决这个问题,小芯片设计人员可能会转向非相干和相干互连 IP,因为这两种 NoC 都支持广泛的协议。

如果芯片设计人员选择使用互连 IP,他们可以自己实现封装/解封装 IP,并从第三方供应商处获得链路层和物理层 IP。或者,封装/解封装 IP 与链路层和 PHY IP 捆绑在一起。还有一种情况是,NoC 供应商将封装/解封装 IP 作为模块提供。

无论细节如何,小芯片和多芯片系统在成本、良率、灵活性、可扩展性和定制方面具有无数优势,因此成为电子设计未来的潮流已变得越来越明显。正当我们认为事情不会变得更令人兴奋时……他们做到了!